[ad_1]

Eletrnica

Redação do Site Inovação Tecnológica – 20/10/2025

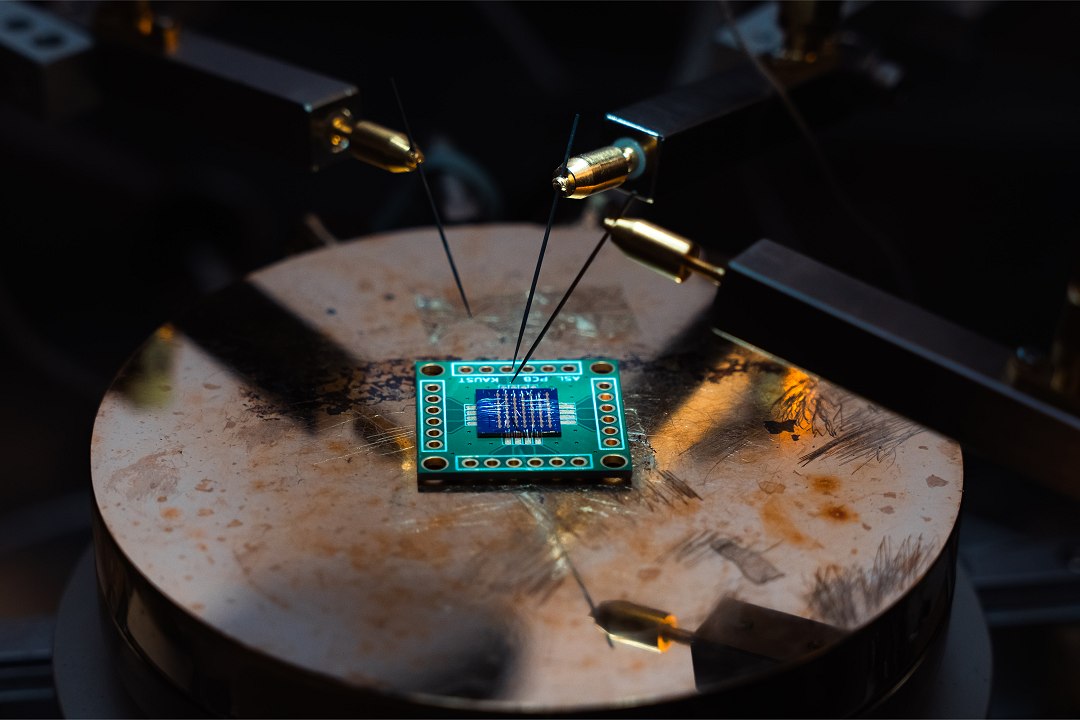

Prottipo do processador de seis andares: o recorde inteiro na fabricao e empilhamento de transistores semicondutores.

[Imagem: KAUST]

Chip 3D de seis andares

Com a crescente aproximao dos limites dos componentes eletrnicos, uma das principais estratgias para aumentar a velocidade dos computadores est na fabricao de chips 3D, criando estruturas empilhadas que diminuem o tempo necessrio para que os dados desloquem-se de um componente para outro.

Os chips em formato de sobrado – com dois andares – j so comuns, mas Saravanan Yuvaraja e colegas da Universidade de Cincia e Tecnologia Rei Abdullah, na Arbia Saudita, acabam de detonar todos os recordes desses edifcios eletrnicos.

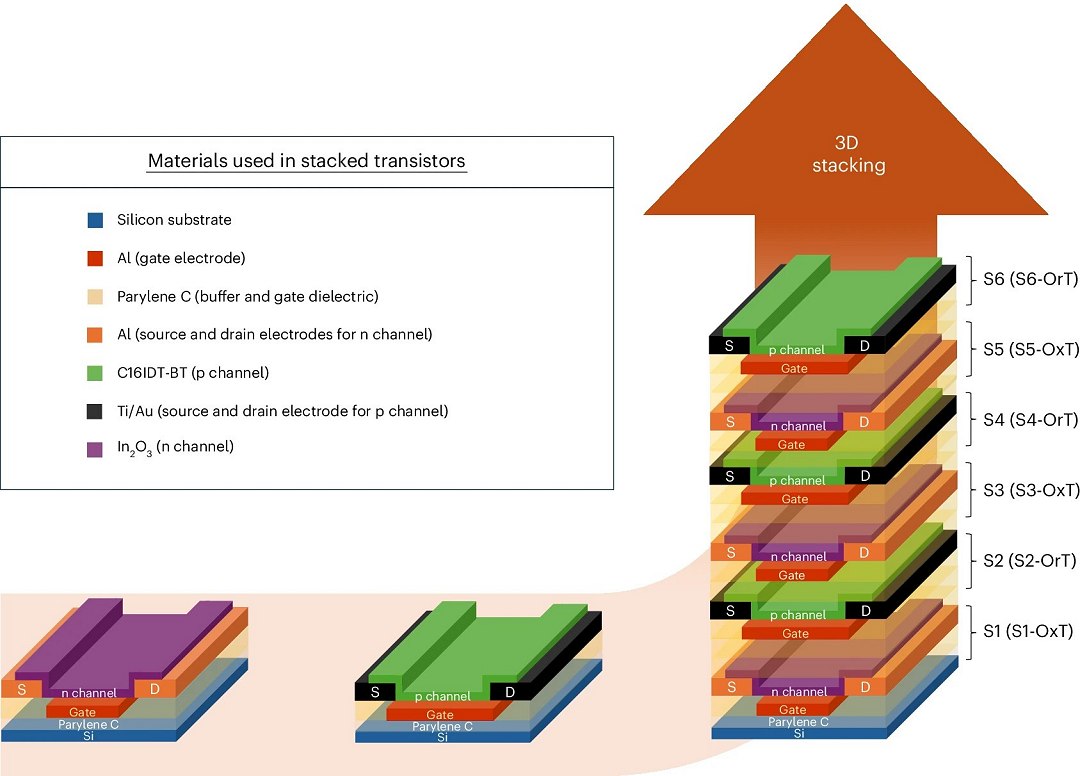

A equipe projetou e construiu o primeiro chip CMOS hbrido de seis camadas para eletrnica de grande porte. Porquê nenhum outro giro integrado hbrido tinha excedido at agora as duas pilhas, nascente feito marca um novo padro em termos de densidade de componentes e eficincia de integrao, abrindo possibilidades em miniaturizao e desempenho da eletrnica.

Entre as tecnologias da microeletrnica, os circuitos integrados CMOS (semicondutor complementar de xido metlico) so encontrados em quase todos os eletrnicos, de celulares e televisores a satlites e dispositivos mdicos. E, comparados aos chips de silcio convencionais, os microchips CMOS hbridos, uma vez que o usado nesta demonstrao, so ainda mais promissores para a eletrnica de grandes reas, colocando mais poder de processamento dentro de cada chip, provendo miniaturizao suplementar e ganhos de velocidade.

A arquitetura usada hbrida, permitindo incorporar os mais recentes avanos na fabricao dos transistores.

[Imagem: Saravanan Yuvaraja et al. – 10.1038/s41928-025-01469-0]

Potncia em menos espao

A fabricao de circuitos integrados tipicamente requer temperaturas de centenas de graus Celsius, o que acaba danificando os andares inferiores do chip 3D medida que novos andares so adicionados. No novo processo, nenhuma lanço de fabricao excedeu 150 C – impedindo danos s camadas anteriormente depositadas – na verdade, a maioria das etapas foi concluda quase temperatura envolvente.

Outra exigncia que a superfcie das camadas deve ser o mais lisa possvel, para que os componentes possam ser depositados de modo perfeitamente desempenado – para o empilhamento vertical funcionar, as camadas devem ser alinhadas corretamente, para uma conexo ideal entre os componentes. Tambm cá a novidade tcnica superou a concorrncia, permitindo chegar aos seis andares.

“No projeto de microchips, tudo envolve reunir mais potncia em menos espao. Ao refinar vrias etapas da fabricao, fornecemos um protótipo para escalar verticalmente e aumentar a densidade funcional muito alm dos limites atuais,” disse Yuvaraja.

Item: Three-Dimensional Integrated Hybrid Complementary Circuits for Large-Area Electronics

Autores: Saravanan Yuvaraja, Mohamad Insan Nugraha, Qiao He, Leo Raj Solay, Patsy Arely Miranda Cortez, Na Xiao, Martin Heeney, Thomas D. Anthopoulos, Xiaohang Li

Revista: Nature Electronics

DOI: 10.1038/s41928-025-01469-0

Outras notcias sobre:

[ad_2]

VEJA MAIS NO CRIADOR DESSE CONTEÚDO by [author_name]